# Low-Side MOSFET Drivers Application and Lab Evaluation

the **puwer** franchise

Mark Dennis Staff Engineer

www.fairchildsemi.com

- Overview of low-side driver applications

- Clamped Inductive switching

- Synchronous rectifier switching

- Transformer drive applications

- Discrete and integrated driver solutions

- Driver datasheet current ratings

- Techniques for evaluating driver current capability in the lab

the

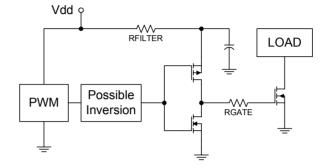

- Direct low-side driver in PWM controller

- PWM output in low to mid power applications (100 to 200W)

- Flyback, boost, forward applications

- When is PWM onboard driver acceptable?

- MOSFET switching times provide acceptable efficiency

- Control circuit not disrupted by noise

- Heat dissipation is within acceptable limits

- When are external drivers needed?

- Higher power requires more current capability

- Need translation from logic levels to higher gate drive voltage

- IGBTs need high voltage drive (>15V)

- Grounding, noise and heat issues affect operation

- Application requires driving gate or pulse transformers

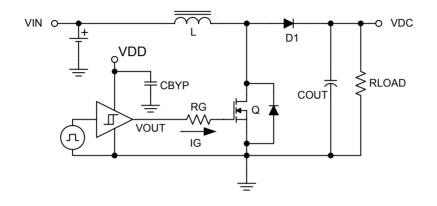

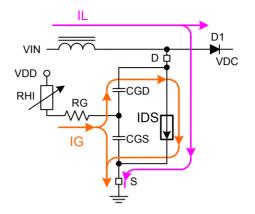

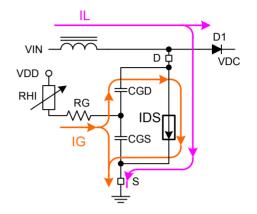

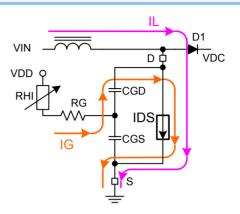

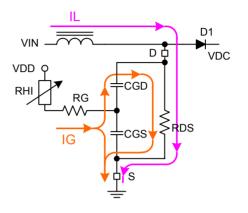

#### Examine Boost with Clamped Inductive Load

- Non-isolated boost stage

- Illustrates clamped inductive load switching

- Inductor L is large, constant current during switching intervals

- Switching intervals are examined in following slides as in [1], [2]

- Allow user to estimate I<sub>G</sub> requirements

the

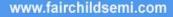

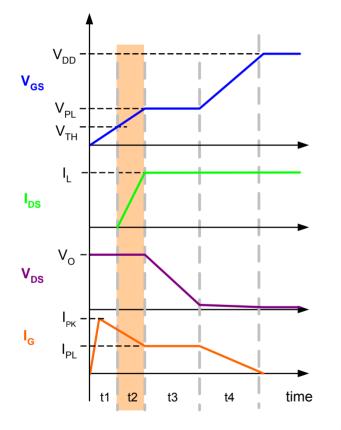

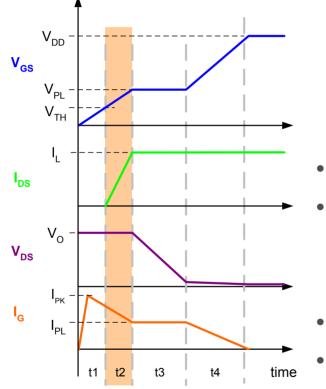

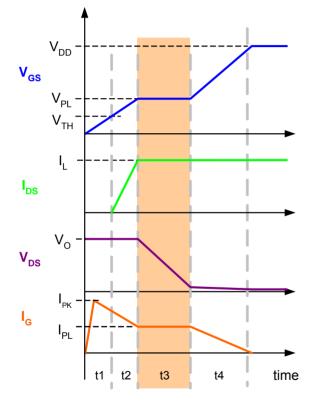

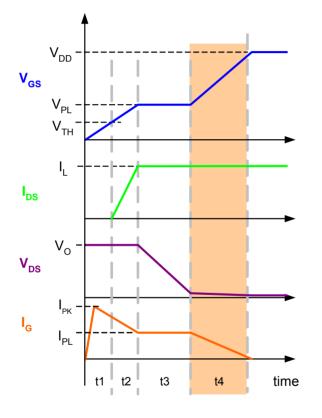

## MOSFET Turn on in Interval t1

- Initially MOSFET is off,  $V_{DS} = V_{OUT}$

- I<sub>G</sub> charges C<sub>GS</sub>||C<sub>GD</sub> to V<sub>TH</sub>

- I<sub>G</sub> amplitude is limited by

- driver output current capability

- external resistance

- parasitic inductance

#### MOSFET Turn on Interval t2

• V<sub>TH</sub> is exceeded and MOSFET starts conducting in linear mode:

$$I_D = g_m (V_{gs} - V_{TH})$$

- I<sub>DS</sub> rises in MOSFET channel from 0 to I<sub>L</sub>

- During t2 C<sub>GD</sub> and C<sub>GS</sub> are charged to a level:

the

tra

nchise

$$V_{PL} = \frac{I_L}{g_m} + V_{TH}$$

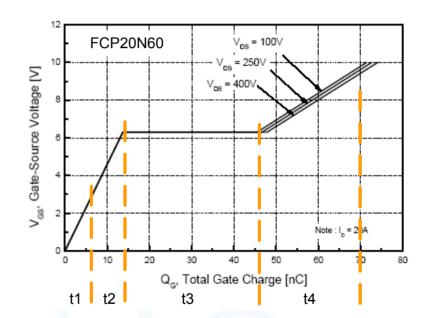

#### What is the Length of Interval t2?

- $I_{DS}$  rises in MOSFET channel from 0 to  $I_{L}$

- t2 interval length can be defined as

$$t2 = T_{IDS,rise} = \frac{Q_{gs2}}{I_G}$$

- Q<sub>GS2</sub> specified by MOSFET datasheet

- I<sub>G</sub> is the current delivered during t2

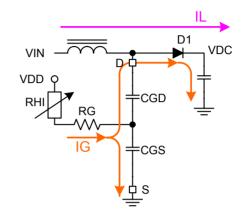

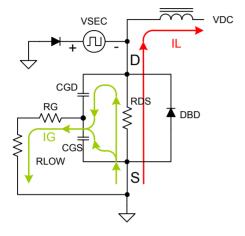

#### Interval t3 – Known as "Miller" region

- I<sub>G</sub> flows through C<sub>GD</sub> while V<sub>GS</sub> remains at V<sub>PL</sub>

- MOSFET conducts full I<sub>L</sub> while V<sub>DS</sub> falls from V<sub>DC</sub> toward GND

- How can we determine driver current capability (Amps) required?

#### What is the Length of Interval t3?

• t3 interval approximated by

$$t3 = T_{vds,f} = \frac{Q_{GD}}{I_G}$$

- Q<sub>GD</sub> derived from MOSFET datasheet

- I<sub>G</sub> is a function of

- driver current source capability

- external impedances

## MOSFET Turn on Interval t4

- $V_{GS}$  rises from  $V_{PL}$  to  $V_{DD}$

- $I_G$  charges  $C_{GD}||C_{GS}$

- R<sub>DS</sub> reaches low value

- $t1 V_{GS}$  reaches  $V_{TH}$  (3V)

- $t2 V_{GS}$  reaches  $V_{PL}$  (6.2V)

- t3 Q<sub>GD</sub> delivered as V<sub>DS</sub> swings low (32 nC)

- $t4 V_{GS}$  enhanced to 9.5V with  $Q_{G,T} = 70 \text{ nC}$

- Average current from  $V_{DD}$  is  $I_{DD} = Q_G \ge f_{SW}$

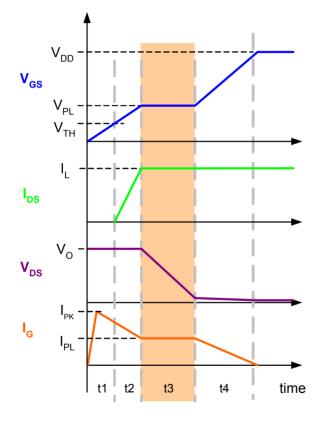

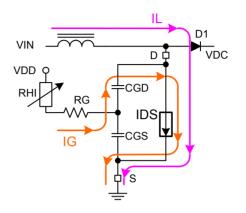

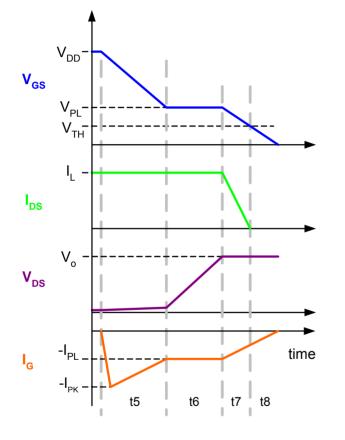

#### Boost Turn off waveforms

- Turn off proceeds in reverse order from turn on

- t5  $V_{GS}$  discharges to  $V_{PL}$

- $t6 I_G$  constant as  $V_{DS}$  rises

- $t7 V_{GS}$  decrease reduces  $I_{DS}$

the

tranchise

•  $t8 - V_{GS}$  is discharged to 0V

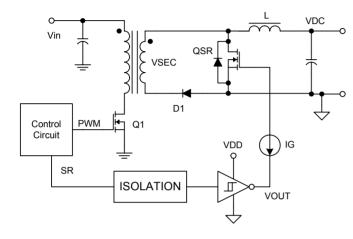

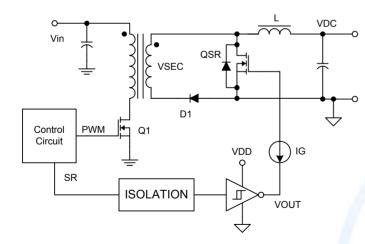

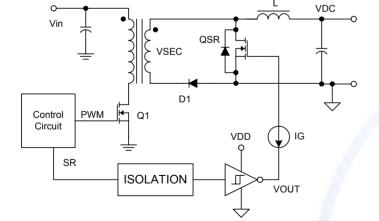

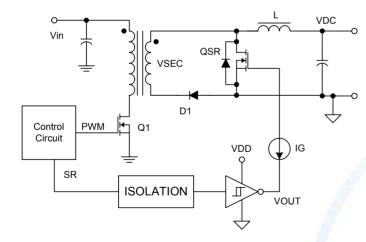

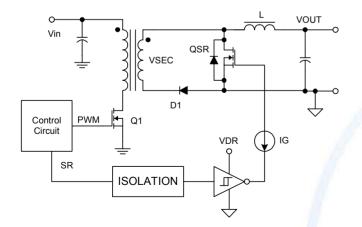

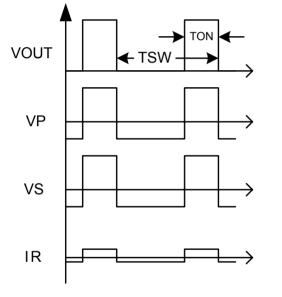

#### Forward Converter with Secondary Sync. Rectifier

- Simplified forward converter with freewheel diode replaced by Q<sub>SR</sub>

- Q<sub>SR</sub> conducts when Q1 is off

- $Q_{SR}$  must turn off before Q1 turns on

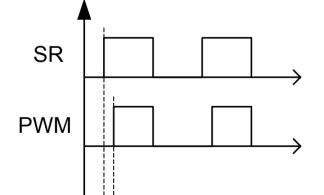

- SR signal leads PWM as indicated

- SR signal generation

- primary controller

- external timing circuitry

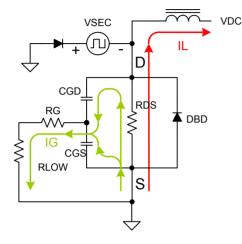

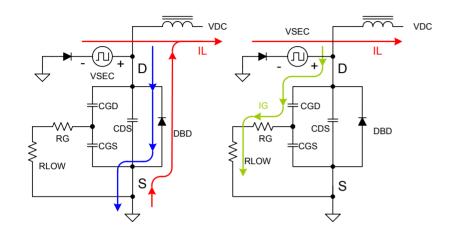

## SR MOSFET Turn off operation

- Initially, inductor current flows through MOSFET channel R<sub>DS</sub>

- Driver output goes low and sinks current I<sub>G</sub> shown

- In many applications there is no external resistor between driver and MOSFET

- How can we determine driver current capability (Amps) required?

the

tra

## What Driver is Needed for SR MOSFET?

Turn-off time can be estimated using Q<sub>Q,SR</sub> as determined in [3]

$$t_{off} = \frac{Q_{Q,SR}}{I_G}$$

With

$$Q_{Q,SR} = (C_{GS} + C_{GD,SR}) \cdot V_{DRV}$$

$$C_{GD,SR} = 2 \cdot C_{RSS,SPEC} \cdot \sqrt{\frac{V_{DS,SPEC}}{0.5 \cdot V_{DRV}}}$$

$$C_{GS} = C_{ISS} - C_{RSS}$$

- C<sub>ISS</sub> and C<sub>RSS</sub> found on datasheet curves, C<sub>GS</sub> approximately constant

- What value should be used for I<sub>G</sub>?

- With MOSFET OFF,  $I_L$  flows through body diode  $D_{BD}$

- This current flow is determined by external circuit, not MOSFET gate-source voltage

the

tranchise

• No gate current flows

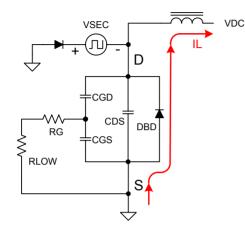

#### SR MOSFET dV/dT interval

- $V_{SEC}$  polarity switches as shown with  $V_{SEC}$  (-) clamped by diode

- This forces reverse recovery current (blue) through body diode and I<sub>L</sub> transfers to V<sub>SEC</sub> (left)

- After  $D_{BD}$  recovers  $V_{DS}$  rises

- With no current in C<sub>GS</sub>, driver sinks current (right)

the

Tra

nchise

$$I_G = C_{GD} \cdot \left(\frac{dV_{DS}}{dT}\right)$$

www.fairchildsemi.com

- Gate drive transformer applications

- Higher power converters often have high/low switches

- High voltage or primary-secondary isolation may be needed

- Short propagation delays resulting from small leakage inductance improves protection [4]

- Competition: half-bridge gate drive ICs

- Pulse transformers used for communication

- communication needed for enhanced performance

- competition: high speed opto-isolators with digital outputs

- These two applications can look similar

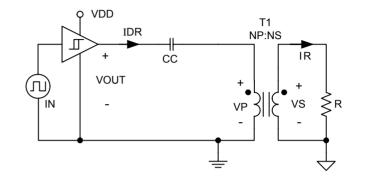

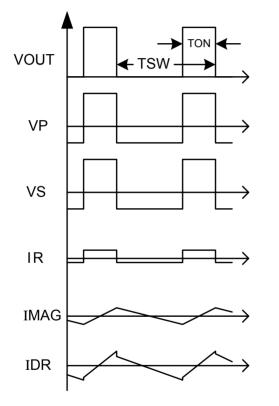

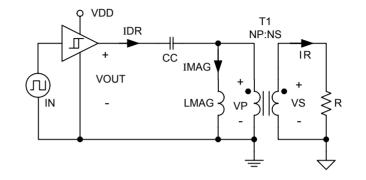

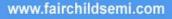

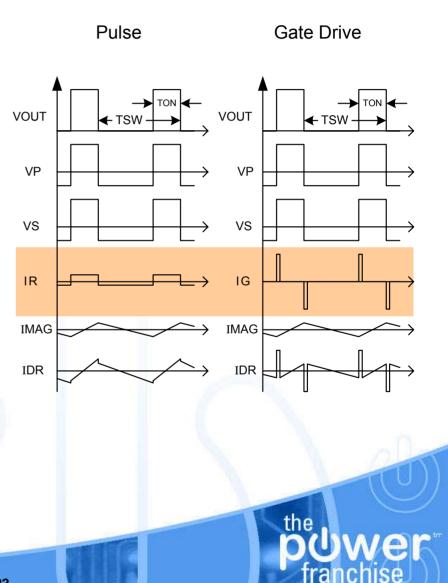

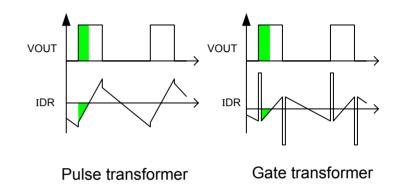

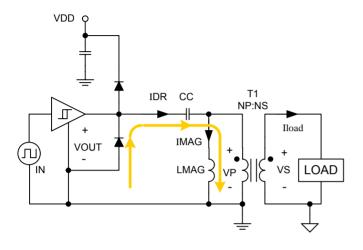

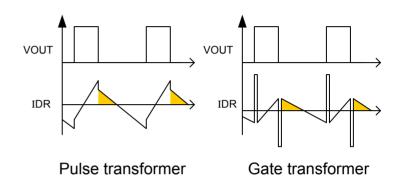

## Pulse Transformer With Resistive Load

- V<sub>OUT</sub> has DC voltage component

- Transformer cannot support DC voltage

- C<sub>c</sub> blocks DC voltage but passes AC

- C<sub>C</sub> selected with ripple voltage <<V<sub>OUT</sub> while passing  $I_{DR}$

- With Np=Ns, V<sub>P</sub> and V<sub>S</sub> are centered at 0V and amplitudes change with duty cycle

- Positive Volt-sec = negative Volt-sec

# Pulse Transformer With Resistive Load-2

- Transformer is replaced by magnetizing inductance in parallel with ideal transformer

- I<sub>DR</sub> is equal to magnetizing current I<sub>MAG</sub> plus reflected resistive current I<sub>R</sub>

- I<sub>MAG</sub> is defined by L<sub>MAG</sub>, voltage, and time (not load)

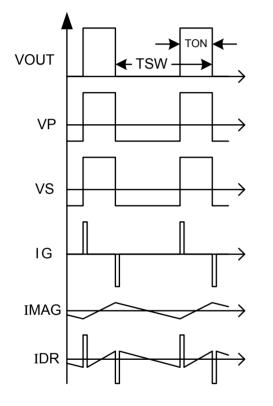

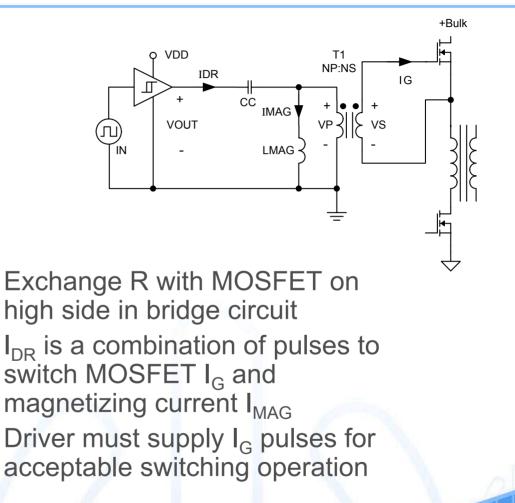

# Change to MOSFET Gate Drive Application

the

franchise

21

- For these applications  $V_{\text{OUT}},\,V_{\text{P}},\,V_{\text{S}},\,$  and  $I_{\text{MAG}}$  are the same

- $I_R$  and  $I_G$  are very different

- Winding DC resistance (DCR) should be checked for voltage drop and losses

- Same transformer often works in either circuit

- Transformer E-T Product (V-us) calculated on secondary side

## Driver Reverse Current - $V_{OUT}$ High

the

tra

- Before  $V_{\text{OUT}}$  goes HIGH,  $I_{\text{MAG}}$  is negative and driver sinks current

- When V<sub>OUT</sub> goes HIGH driver must continue to sink current

- Bipolar drivers need external diodes, MOSFET drivers can conduct reverse current through channel, body diode

#### **Driver Reverse Current Vout - Low**

the

tra

- Before  $V_{\text{OUT}}$  goes LOW,  $I_{\text{MAG}}$  is positive and driver sources current

- When V<sub>OUT</sub> goes LOW driver must continue to source current

- Bipolar drivers need external diodes, MOSFET drivers can conduct reverse current through channel, body diode

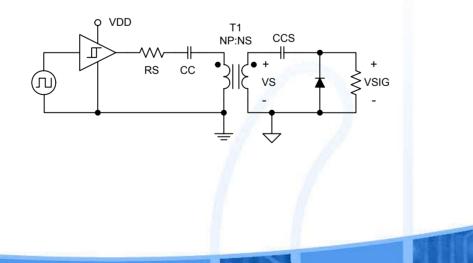

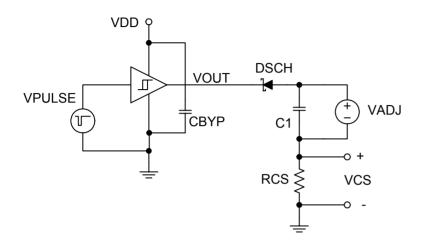

- In initial pulse transformer circuit  $V_{\rm S}$  is related to  $V_{\rm DD}$  by turns ratio, and varies with duty cycle

- $C_{CS}$  and D clamp V<sub>SIG</sub> with GND reference

- $C_C$  and  $L_{MAG}$  undergo startup transient

- Series R<sub>S</sub> can be selected to provide critical damping

$$R_{S} = 2 \cdot \sqrt{\frac{L_{MAG}}{C_{C}}}$$

the

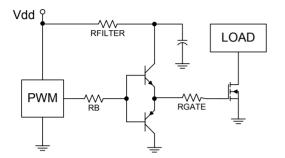

- Discrete designs built from bipolar or MOSFET devices

- Integrated circuit devices using bipolar, MOSFET, or compound (combined) device technologies

- All driver applications benefit from:

- Local bypass capacitor

- filtering from control circuit Vdd

- location close to load

- capability to dissipate power

#### **Discrete Driver Configurations**

the

- NPN/PNP emitter follower

- Non-inverting configuration works directly in phase with control chip

- No shoot-thru, devices not on simultaneously

- Output has no ohmic connection to rails

- PMOS/NMOS driver (inverter)

- Natural inversion requires additional inversion to follow control

- Overlap in V<sub>GS</sub> conduction range leads to shoot-thru

- Rail to rail operation

- More individual devices needed in circuit

- assembly and test time grow

- more reliability concerns

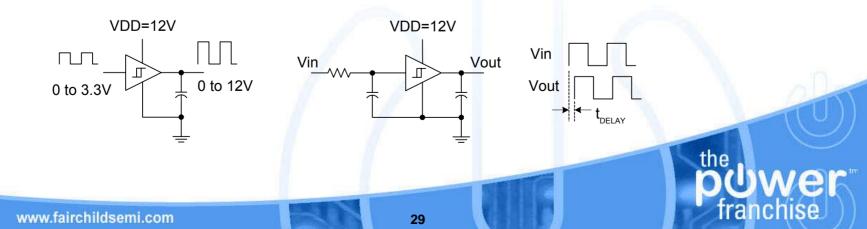

- Translation from logic level inputs to higher voltage drive levels adds complexity

- For fast switching, input driving signal needs fast edges (output not fully buffered from input)

- Difficult to introducing delay through drive stage while keeping fast edge rates

- MOS shoot-thru power loss increases with frequency

- Integrated features can reduce supporting circuitry

- enable functions can simplify control in SR applications

- UVLO can provide orderly startup in secondary side circuits

- Facilitates direct translation from TTL inputs to higher  $V_{GS}$

- High impedance inputs with CMOS thresholds facilitate programming time delay in driver (HIGH =  $2/3 V_{DD}$ , LOW =  $1/3 V_{DD}$ )

- Device input current usually negligible

- Small MLP packages enable highest density designs

- dual 2 A, 4 A drivers in 3x3 mm ; single 2 A in 2x2 mm

- thermal pads allow reduced thermal impedance

- Summary: Less component level design required from users

- Many users treat drivers as near-ideal signal amplifiers

- Some assumptions may not be justified:

- Sink and source current defined by series resistances

- Output slew rates are instantaneous

- Output current varies with V<sub>DD</sub>, parasitic impedances, size of external load, temperature, other factors

- Output rise/fall specifications don't give much insight into instantaneous current capability

- Current specified in one of several ways

- Peak current available from driver

- Current available with output at clamped voltage level

- Current available through low value resistance (or short circuit)

- Measure current with current probe bandwidth, inductance concerns

- All driver measurements require attention to detail!

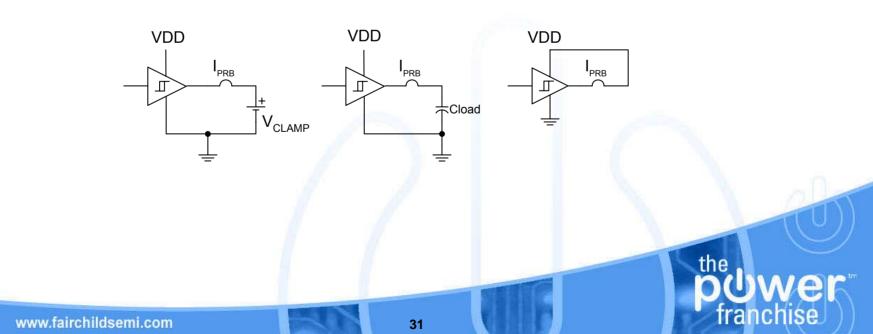

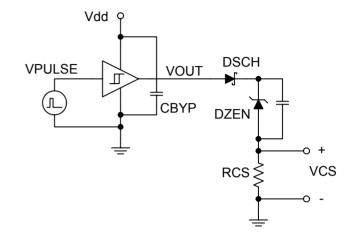

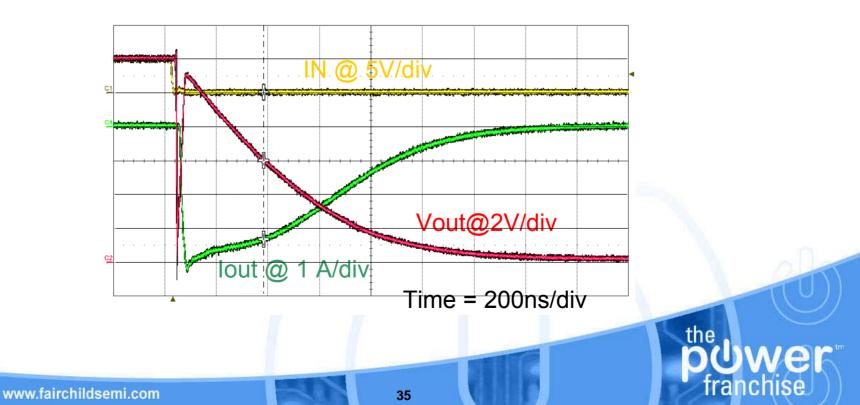

## **Clamped Circuits for Pulsed Testing**

the

tra

nchise

- These circuits test current capability for pulses of 200ns with <u>minimal</u> external resistance ( $R_{CS}$  is 0.05  $\Omega$ )

- With good layout, transient dies out < 100ns

- $V_{PULSE}$  is 200ns pulse at low duty cycle, 2%

- At left  $I_{SINK}$  is monitored as  $V_{CS}$  goes negative

- On right  $I_{SOURCE}$  is monitored as  $V_{CS}$  is positive

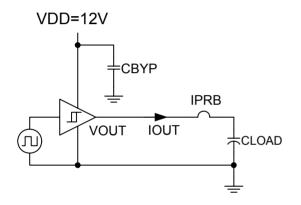

- $I_{\text{PRB}}$  monitors  $I_{\text{OUT}}$  charging or discharging a large capacitor

- C<sub>LOAD</sub> chosen as 100x capacitor used in rise/fall time specs

- 2 Amp 100 x 1nF = 0.1uF

- 4 Amp 100 x 2.2nF = 0.22uF

- This allows measurement of  $I_{\text{OUT}}$  at various values of  $V_{\text{OUT}}$

- This is maximum current available from driver with <u>NO</u> external resistance

- This equates to the pulse current values obtained in clamped sink and source circuits

the

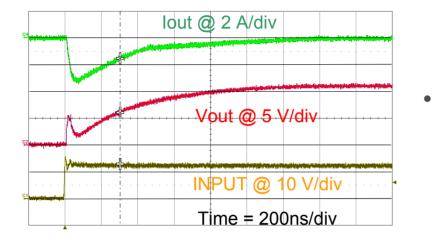

# Look at 2 Amp Drivers with Large Load

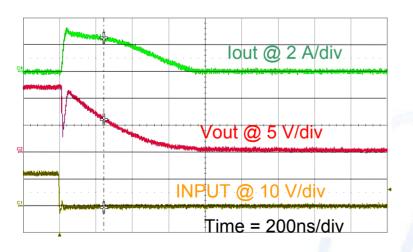

- Top picture FAN3227C I<sub>SOURCE</sub>

- Approximately 3 Amps I<sub>OUT,peak</sub>

- I<sub>SOURCE</sub> = 1.5 Amps @ 6V<sub>OUT</sub>

- Bottom picture FAN3227C ISINK

- Approximately 3 Amps I<sub>OUT,peak</sub>

the

tranchise

- I<sub>SINK</sub> = 2 Amps @ 6V<sub>OUT</sub>

- Note initial transient due to current loop inductance (<100ns)</li>

- MOS-based drivers spec peak current and R<sub>DS,high</sub> or R<sub>DS,low</sub>

- The R<sub>DS, on</sub> values not achieved during early stages of turn on

- Peak current is significantly less than I=V<sub>DD</sub>/R<sub>DS</sub>

- In examples tested, datasheet current rating is peak current available from device

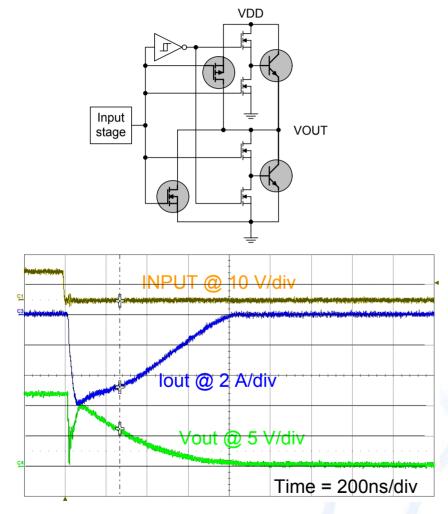

## Integrated Driver with Compound Output Stage

- Compound output stage

combines bipolar and MOSFET

- Bipolars provide current during mid range of V<sub>OUT</sub> and clamp V<sub>OUT</sub> within 1 volt of rails

- MOSFETs pull V<sub>OUT</sub> to rails and offers bi-directional current capability

- FAN3224C shows 6 Amp I<sub>SINK,pk</sub>

- FAN3224C sinks 4.5 Amps at V<sub>OUT</sub> = 6V (datasheet says 4 Amp driver)

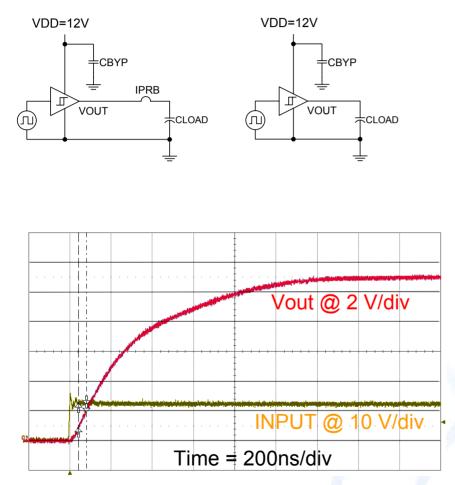

#### Now Remove Current Probe

- I<sub>PRB</sub> requires wire loop for current probe

- C<sub>LOAD</sub> is surface mount 0.1uF, (0805) with minimal inductance

- Note lack of initial transient!

- Calculate current from familiar equation applied over short, approximately linear interval.

$$I = C_{LOAD} \cdot \left(\frac{dV_{OUT}}{dT}\right)$$

$$I = 0.1\mu F \cdot \left(\frac{1.131V}{40.6ns}\right) = 2.8A$$

the

tranchise

- Key low-side driver applications include

- ground referenced switches

- SR applications

- pulse and gate drive transformer applications

- Potential drivers include integrated and discrete

- PMOS-NMOS drivers

- bipolar drivers

- compound drivers which combine bipolar and MOSFET

- Lab evaluation of drivers current capability

- presented progression of pulse and "large load" circuits

- correlated lab data provide confidence in results

- [1] 2006 Fairchild Power Seminar Topic, "Understanding Modern Power MOSFETs," http://www.fairchildsemi.com/powerseminar/pdf/understanding\_modern\_power\_mOSFETs.pdf

- [2] Oh, K. S., "MOSFET Basics", July, 2000, available as AN9010 from the fairchildsemi.com webite

- [3] Balogh, L. "Design and Application Guide for High Speed MOSFET Gate Drive Circuits," Power Supply

Design Seminar SEM-1400, Topic 2, Texas Instruments Literature No. SLUP169

- [4] ICE Components Gate Drive Transformer Datasheet "GT03.pdf" dated 10/06, available from www.icecomponents.com

- [5] 2006 Fairchild Power Seminar Topic, "Practical Power Application Issues for High Power Systems,"

http://www.fairchildsemi.com/powerseminar/pdf/practical\_power\_high\_power\_systems.pdf

[6] Johnson, H. Dr, "High-Speed Digital Design On-Line Newsletter," Vol. 3 Issue 8,

www.sigcon.com/Pubs/news/3\_8.htm